Бінарна інформація, реалізована за допомогою МОН-транзисторів

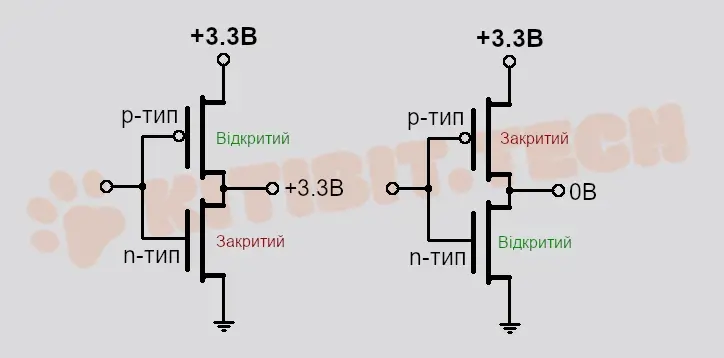

Інформація в комп'ютерних системах зберігається і обробляється у вигляді рівнів напруги. Високий рівень напруги вважається '1', низький - '0'. На малюнку нижче зображено схему типового комплементарного метал-оксидного напівпровідника. Простими словами це два польових транзистора (p-типу і n-типу), виготовлених як єдиний компонент за спеціальною технологією (CMOS). Зліва на виході 3,3В (високий рівень - '1'), справа - 0В (низький рівень - '0').

В реальних умовах, високий та низький рівні це не конкретні значення, а деякі діапазони напруг. Наприклад, від 2 вольт до 5 вольт - високий рівень, від 0 до 1.3 вольт - низький. Завдяки проміжку в 0.7В (між 1.3В і 2В) дозволяє пристроям працювати швидко з високою точністю. Ці діапазони можуть різнитись від пристрою до пристрою. Звісно, проектування цифрових схем на транзисторному рівні виходить за рамки цієї статті, однак важливо знати, що цифрові дані існують у вигляді двійкових бітів і закодовані як висока та низька напруга.

В реальних умовах, високий та низький рівні це не конкретні значення, а деякі діапазони напруг. Наприклад, від 2 вольт до 5 вольт - високий рівень, від 0 до 1.3 вольт - низький. Завдяки проміжку в 0.7В (між 1.3В і 2В) дозволяє пристроям працювати швидко з високою точністю. Ці діапазони можуть різнитись від пристрою до пристрою. Звісно, проектування цифрових схем на транзисторному рівні виходить за рамки цієї статті, однак важливо знати, що цифрові дані існують у вигляді двійкових бітів і закодовані як висока та низька напруга.

Максимальна напруга на вході, яка сприймається як низька позначається VIL (від Voltage Input Low). Мінімальна вхідна напруга, що сприймається як висока позначається VIH (від Voltage Input High). Відповідно вихідна максимально низька - VOL, вихідна мінімальна висока - VOH. Ця інформація вказується в документації пристрою (datasheet).

Коли необхідно обробляти інформацію, яка має більше 2 станів використовують набір бітів. Так, два біти може мати 4 стани (00, 01, 10, 11), а 3 біти можуть мати 8 станів (000, 001, 010, 011, 100, 101, 110, 111). В цілому, n бітів має 2n станів (комбінацій). Про математичні основи бінарної системи можна почитати в цій статті Бінарна система числення

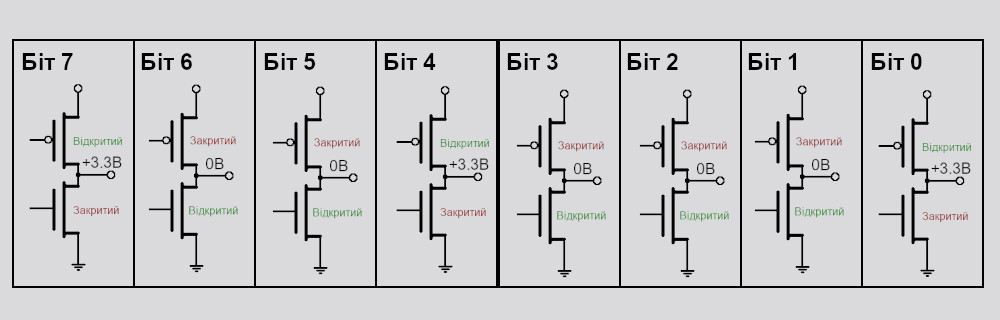

Один байт це набір з 8 біт, виконаних у вигляді єдиного "об'єкта":

Інформація має багато форм: числа, логічні стани, текст, машинні інструкції, звук або зображення. Що саме означають біти залежить від того, як організована інформація, і, що ще важливіше, як вона інтерпретується. На цьому рисунку показано один байт у стані, що представляє двійкове число 10010001. Знову ж таки, вихідна напруга 3.3 В означає «істина» або 1, а вихідна напруга 0 В означає «хибність» або 0.

Цифрова логіка

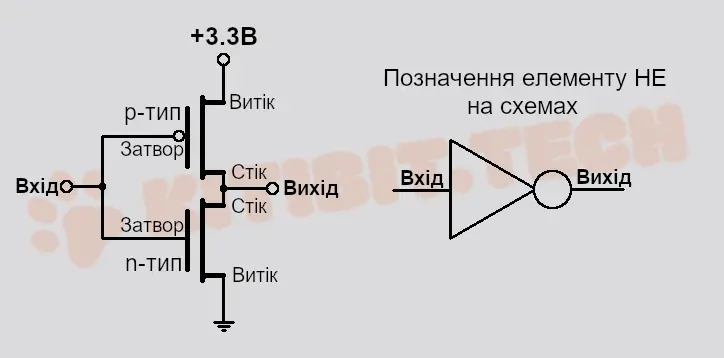

У цьому розділі ми трохи розглянемо, як працює цифрова логіка комп'ютера. Транзистори, виготовлені з металоксидних напівпровідників, називаються МОН-транзистори. У цифровому світі МОН-транзистори можна розглядати як перемикачі, керовані напругою. Схеми, виготовлені з МОН-транзисторами як p-типу, так і n-типу, називаються комплементарними металоксидними напівпровідниками або КМОН (CMOS). На малюнку нижче представлено КМОН-вентиль, який діє як логічний оператор "НЕ" - якщо на вході 1 (високий рівень), то на виході 0 (низький рівень) і навпаки:

Щоб зрозуміти як працюють схеми на CMOS-транзисторному рівні треба знати декілька речей. Кожен транзистор діє як перемикач - струм протікатиме від витоку до стоку коли транзистор відкритий, і струм не протікатиме коли транзистор закритий. Транзистор відкривається і закривається напругою на затворі. Транзистори p-типу закриваються при подачі напруги високого рівня на затвор і відкриваються коли напруга на затворі низького рівня. Транзистори n-типу відкриті коли на затворі високий рівень і закриті, якщо на затворі низький рівень. Розглянемо два можливі варіанти схеми на рисунку вище. Якщо на вході високий рівень (+3,3 В), то p-транзистор вимкнений і напруга живлення через нього не проходить до виходу, а n-транзистор активний і замикає вихід на землю, роблячи його низьким (0 В). І навпаки, якщо на вході низький рівень (0 В), то p-транзистор відкритий, а n-транзистор закритий. Через витік-стік p-транзистора на вихід подається високий рівень (+3,3 В).

Щоб зрозуміти як працюють схеми на CMOS-транзисторному рівні треба знати декілька речей. Кожен транзистор діє як перемикач - струм протікатиме від витоку до стоку коли транзистор відкритий, і струм не протікатиме коли транзистор закритий. Транзистор відкривається і закривається напругою на затворі. Транзистори p-типу закриваються при подачі напруги високого рівня на затвор і відкриваються коли напруга на затворі низького рівня. Транзистори n-типу відкриті коли на затворі високий рівень і закриті, якщо на затворі низький рівень. Розглянемо два можливі варіанти схеми на рисунку вище. Якщо на вході високий рівень (+3,3 В), то p-транзистор вимкнений і напруга живлення через нього не проходить до виходу, а n-транзистор активний і замикає вихід на землю, роблячи його низьким (0 В). І навпаки, якщо на вході низький рівень (0 В), то p-транзистор відкритий, а n-транзистор закритий. Через витік-стік p-транзистора на вихід подається високий рівень (+3,3 В).

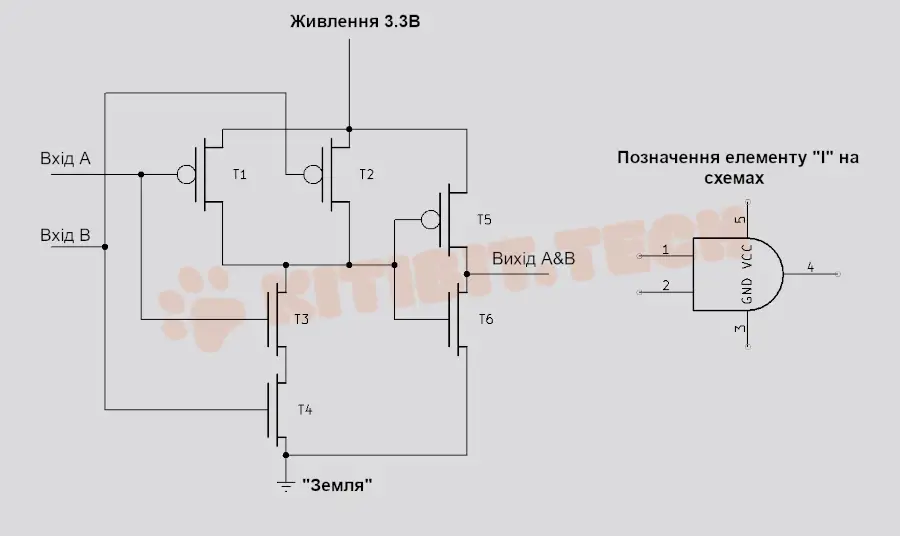

Цифрові логічні елементи, такі як "І", "АБО" та "ВИКЛЮЧНЕ АБО" приймають два входи та видають один вихід. На малюнку зображено схему логічного елементу "І", який на виході встановлює високий рівень тоді і тільки тоді, коли на обох входах високі рівні:

Ми можемо зрозуміти роботу елемента "І", спостерігаючи за поведінкою його шести транзисторів. Якщо обидва входи A та B мають високий рівень, T3 та T4 будуть активними. Крім того, якщо A та B мають високий рівень, T1 та T2 будуть вимкнені. У цьому випадку рівень на вхід Т5-Т6 буде низьким, оскільки комбінація перемикачів T3–T4 замкне цей сигнал на землю. Пара Т5-Т6 працюють як "НЕ", обертаючи сигнал на протилежний, тому в результаті на виході отримаємо високий рівень. Якщо A має низький рівень, T1 буде активним, а T3 вимкненим. Аналогічно, якщо B має низький рівень, T2 буде активним, а T4 вимкненим. Тому, якщо A або B має низький рівень - рівень на вході Т5-Т6 буде високим, оскільки один або обидва перемикачі T1, T2 замкнуть цей сигнал на +3,3 В. І в результаті обернення сигналу на Т5-Т6 на виході схеми буде низький сигнал.

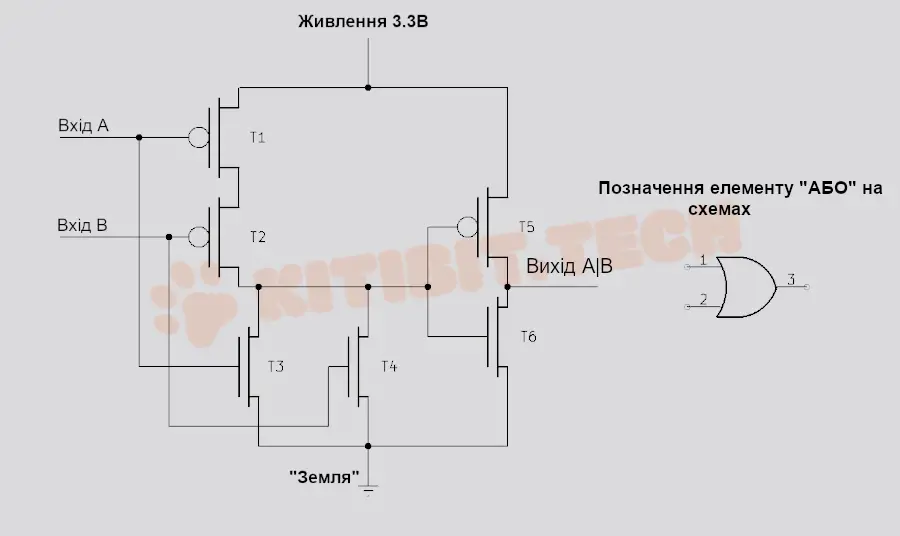

Також розглянемо логічний елемент "АБО", який на виході встановлює високий рівень, коли на один з двох входів (або на обидва) подано високий рівень:

Ми можемо зрозуміти роботу елемента АБО, спостерігаючи за поведінкою його шести транзисторів. Якщо обидва входи A та B мають низький рівень, T1 та T2 будуть активними (відкритими), при цьому T3 та T4 будуть закритими. У цьому випадку сигнал на вході Т5-Т6 буде високим, а на виході низьким. Якщо A має високий рівень, T3 буде активним, а T1 вимкненим. Аналогічно, якщо B має високий рівень, T4 буде активним, а T2 вимкненим. Тому, якщо A або B (або обидва) має високий рівень, сигнал на вході Т5-Т6 буде низьким, оскільки один або обидва перемикачі T3, T4 замкнуть цей сигнал на землю і вихід з Т5-Т6 відповідно буде високим.

Коли ми пишемо програмне забезпечення, маємо два типи логічних операцій. При роботі з числами (набором бітів) логічні операції виконуються побітово. Іншими словами, операція застосовується незалежно до кожного біта. У мові C логічний побітовий оператор "І" позначається символом &. Наприклад:

якщо A = 01100111,

а B = 11110000,

тоді A&B = 01100000Інший тип логічної операції застосовується при роботі з булевими значеннями. У мові C умова false представлена значенням 0, а true — будь-яким ненульовим значенням. У цьому випадку:

якщо булеве A = 01100111,

а B = 11110000,

то обидва вони істинні (true).

Стандартним значенням для true є 1. У C булевий оператор для AND — це &&. Виконання булевої операції дає результат A&&B = 1.

У мові C логічний побітовий оператор для OR позначається символом |. Логічна операція застосовується незалежно до кожного біта. Наприклад:

якщо A = 01100111,

а B = 11110000,

тоді A|B = 11110111

У C булевий оператор для OR — це ||. Виконання булевої операції true OR true дає результат true. Хоча стандартним значенням для істини є 1, будь-яке ненульове значення також вважається істинним. Наприклад:

A = 01100111,

B = 11110000,

тоді A||B = 1.

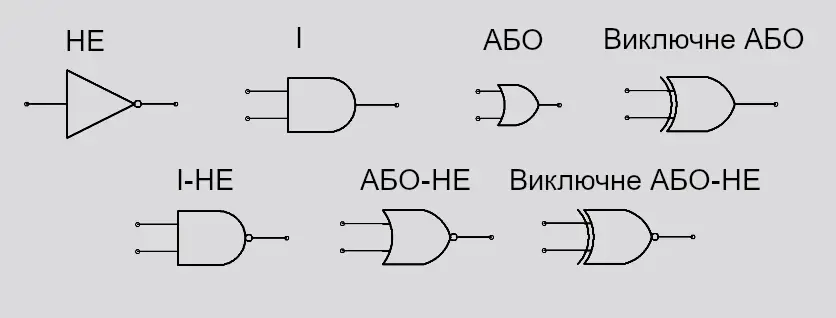

Існують також інші логічні оператори:

- Виключне АБО - на виході високий рівень (одиниця) коли тільки на одному вході високий

- І-НЕ - на виході 0 тільки коли на обох входах високі рівні

- АБО-НЕ - на виході 1 тільки коли на обох входах нулі

- Виключне АБО-НЕ - на виході 1 коли на входах однакові значення.

Виходи всіх логічних елементів для всіх комбінацій на входах відображено в таблиці:

| Вхід A | Вхід B | Вихід І | Вихід І-НЕ | Вихід АБО | Вихід АБО-НЕ | Виключне АБО | Виключ. АБО-НЕ |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

Нижче зображено позначення всіх переглянутих елементів на схемах:

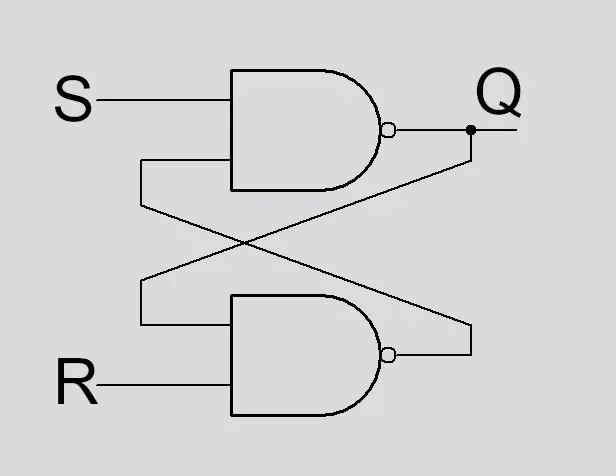

Тригери

Для роботи цифрових схем необхідні цифрові пристрої для зберігання даних, які є ключовими компонентами для побудови регістрів і пам’яті. Найпростішим пристроєм зберігання є тригер типу «set-reset» (SR-тригер). Один зі способів реалізації SR-тригера з допомогою І-НЕ елементів показаний на рисунку:

Якщо на входи подані значення S=0 та R=1, то вихід Q дорівнюватиме 1. Навпаки, якщо S=1 та R=0, то вихід Q дорівнюватиме 0. Зазвичай обидва входи S і R утримуються в стані логічної 1. Щоб установити тригер (Q=1), сигнал S знижують до 0, а потім знову піднімають до 1. Щоб скинути тригер (Q=0), аналогічно знижують сигнал R до 0 і знову піднімають до 1. Якщо обидва входи S і R дорівнюють 1, на виході Q зберігатиметься попереднє значення. Якщо ж обидва сигнали S і R одночасно дорівнюють 0, тригер переходить у непередбачуваний режим.

Якщо на входи подані значення S=0 та R=1, то вихід Q дорівнюватиме 1. Навпаки, якщо S=1 та R=0, то вихід Q дорівнюватиме 0. Зазвичай обидва входи S і R утримуються в стані логічної 1. Щоб установити тригер (Q=1), сигнал S знижують до 0, а потім знову піднімають до 1. Щоб скинути тригер (Q=0), аналогічно знижують сигнал R до 0 і знову піднімають до 1. Якщо обидва входи S і R дорівнюють 1, на виході Q зберігатиметься попереднє значення. Якщо ж обидва сигнали S і R одночасно дорівнюють 0, тригер переходить у непередбачуваний режим.

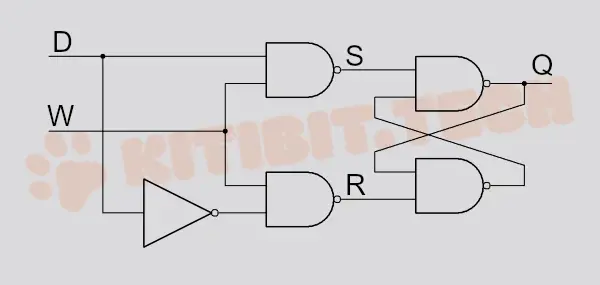

Тригер з керованим входом D (D-защіпка) показаний на рисунку:

Вхідні схеми приймають інформаційний сигнал D та керуючий сигнал W, і формують на їх основі команди S і R для SR-тригера. Наприклад, якщо W=0, тригер перебуває у стані спокою, зберігаючи значення Q, яке було записане раніше. Якщо ж W=1, то в тригер записується значення з входу D. Зокрема, якщо D=1 і W=1, тоді S=0 та R=1, у результаті чого Q=1. Якщо ж D=0 і W=1, тоді S=1 та R=0, у результаті чого Q=0. Таким чином, щоб скористатися D-защіпкою, спочатку на вхід D подається потрібне значення, далі сигнал W переводиться в стан логічної 1, а потім повертається в 0. Це призводить до того, що значення з входу D зберігається на виході Q. Після того як W переходить у 0, сигнал на вході D більше не впливає на стан SR-тригера. Якщо ж вхід D змінюється, поки W залишається в стані логічної 1, то вихід Q змінюється відповідно. Проте останнє значення на вході D запам’ятовується також і у момент спаду сигналу W!

Вхідні схеми приймають інформаційний сигнал D та керуючий сигнал W, і формують на їх основі команди S і R для SR-тригера. Наприклад, якщо W=0, тригер перебуває у стані спокою, зберігаючи значення Q, яке було записане раніше. Якщо ж W=1, то в тригер записується значення з входу D. Зокрема, якщо D=1 і W=1, тоді S=0 та R=1, у результаті чого Q=1. Якщо ж D=0 і W=1, тоді S=1 та R=0, у результаті чого Q=0. Таким чином, щоб скористатися D-защіпкою, спочатку на вхід D подається потрібне значення, далі сигнал W переводиться в стан логічної 1, а потім повертається в 0. Це призводить до того, що значення з входу D зберігається на виході Q. Після того як W переходить у 0, сигнал на вході D більше не впливає на стан SR-тригера. Якщо ж вхід D змінюється, поки W залишається в стані логічної 1, то вихід Q змінюється відповідно. Проте останнє значення на вході D запам’ятовується також і у момент спаду сигналу W!

Існують також тригери типу D (D-тригер), які також використовуються для зберігання інформації. D-тригери є базовими будівельними блоками оперативної пам’яті (RAM) та регістрів у комп’ютері. Щоб зберегти інформацію, спочатку на вхід D подається цифрове значення, яке потрібно запам’ятати, а потім на вхід синхронізації (тактовий вхід) подається фронт сигналу — перехід від 0 до 1. Після цього значення з входу D з’являється на виході Q, і вхід D може змінюватися без впливу на збережене значення. Наприклад, мікросхема 74HC374 є 8-бітним D-тригером, у якому всі 8 бітів зберігаються одночасно під час фронту одного тактового сигналу. За своєю структурою та принципом роботи 74HC374 подібна до регістра — швидкодіючої пам’яті всередині процесора. Якщо вхід дозволу (G) у 74HC374 перебуває в стані логічної 1, її виходи переходять у стан HiZ (високий імпеданс, тобто відключені). Якщо ж вхід G у стані логічного 0, тоді вихідні сигнали відповідають збереженим значенням у тригері. D-тригери працюють за принципом «сприйняття по фронту»: зміни на виході відбуваються саме під час фронту тактового сигналу (перехід від 0 до 1).

Бінарний суматор

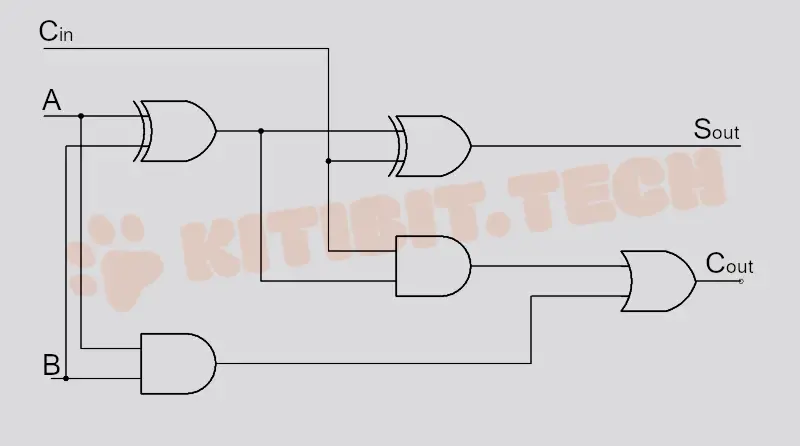

Комп'ютер виконує багато арифметичних та логічних операцій. Ми покажемо одну з них, щоб проілюструвати деякі обчислення, можливі на комп'ютері. Щоб змоделювати схему суматора, почнемо з простої підсхеми, яка називається двійковим повним суматором, як показано на рисунку:

Є два двійкові входи даних A, B та вхід переносу Cin. Є один вихід даних Sout та один вихід переносу Cout. Cin, A та B – це три незалежні двійкові входи, кожен з яких може бути 0 або 1. Ці три входи сумуються (сума може бути 0, 1, 2 або 3), і результат кодується у двобітовому двійковому коді, де Cout є старшим бітом, а Sout – молодшим.

Є два двійкові входи даних A, B та вхід переносу Cin. Є один вихід даних Sout та один вихід переносу Cout. Cin, A та B – це три незалежні двійкові входи, кожен з яких може бути 0 або 1. Ці три входи сумуються (сума може бути 0, 1, 2 або 3), і результат кодується у двобітовому двійковому коді, де Cout є старшим бітом, а Sout – молодшим.

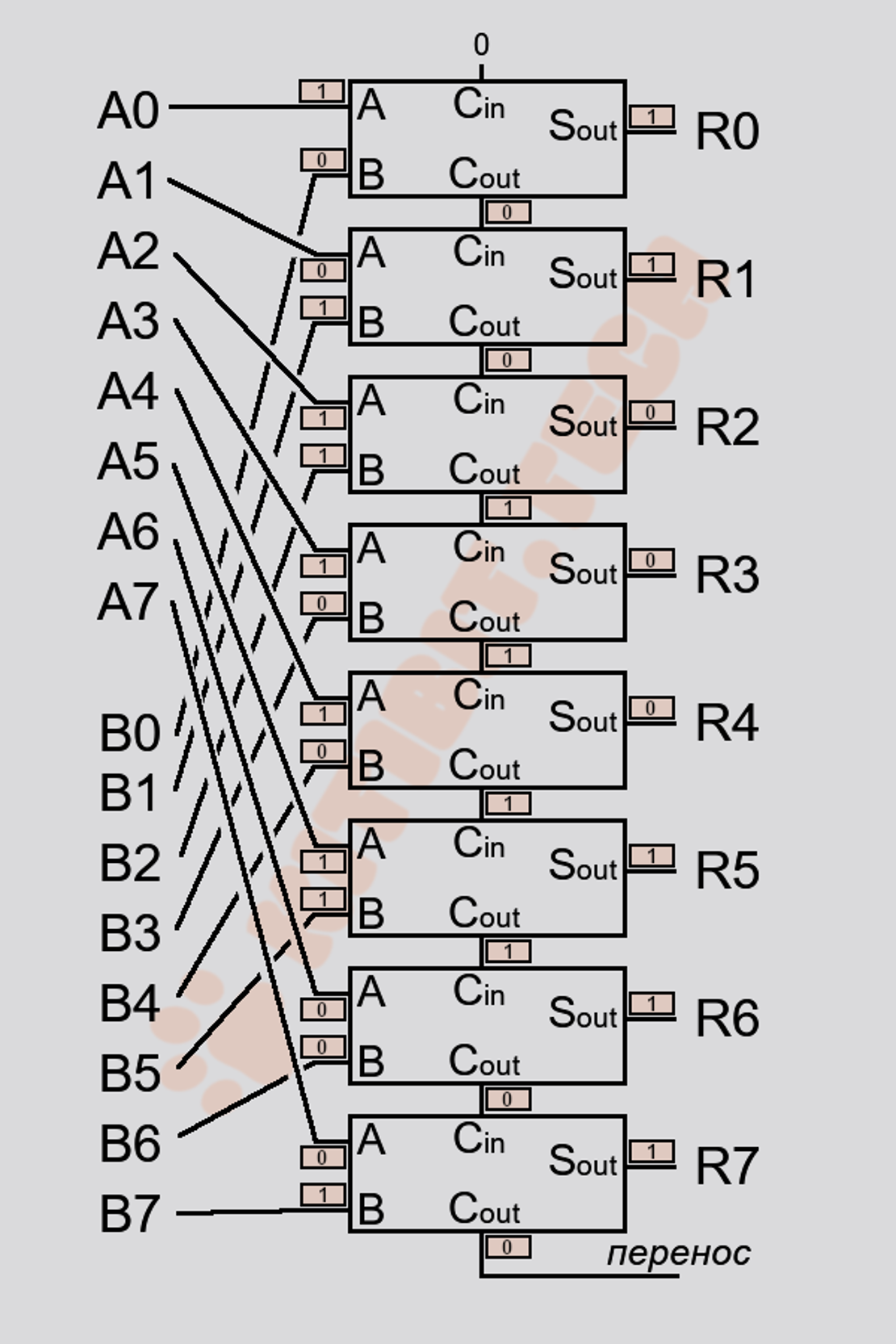

На рисунку зображено 8-бітний суматор, утворений каскадним з'єднанням восьми повних двійкових суматорів (аналогічно будується 32-бітний суматор - каскадуючи 32 повних двійкових суматорів разом).

Для 8-бітного беззнакового числа існує лише 256 можливих значень, які знаходяться в діапазоні від 0 до 255. Коли ми додаємо два 8-бітних числа, сума може бути будь-яким числом від 0 до 510, що є 9-бітним числом. Дев'ятим бітом тут виступає перенос останнього суматора, який по суті означає переповнення - значення результату виходить за межі 8-бітного числа. На схемі вище наведено приклад додавання двох чисел, перенос буде 0:

A = 00111101B = 10100110R = 11100011

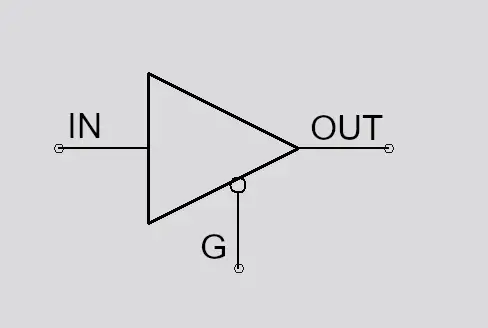

Трьохстановий драйвер

Ще одним важливим компонентом цифрових систем є трьохстановий драйвер (tristate driver) — це електронний елемент, який використовується для керування передачею сигналів у цифрових схемах. Його особливість полягає в тому, що він може перебувати не лише у двох звичних станах (логічний «0» та логічна «1»), а й у третьому — так званому Hi-Z (високоімпедансному стані). На схемах зображається так:

У звичайному режимі, коли драйвер активний (на керуючому вводі G низький рівень), його вихід повторює сигнал на вході: якщо на вході логічна «1», то на виході також буде «1», і навпаки. Проте коли драйвер переведено у неактивний режим (на G високий рівень), він від’єднує свій вихід від кола, наче «відключається». У цьому стані на виході немає ні «0», ні «1» — він перебуває у стані високого опору, тобто фактично не впливає на інші елементи, під’єднані до цієї ж лінії.

У звичайному режимі, коли драйвер активний (на керуючому вводі G низький рівень), його вихід повторює сигнал на вході: якщо на вході логічна «1», то на виході також буде «1», і навпаки. Проте коли драйвер переведено у неактивний режим (на G високий рівень), він від’єднує свій вихід від кола, наче «відключається». У цьому стані на виході немає ні «0», ні «1» — він перебуває у стані високого опору, тобто фактично не впливає на інші елементи, під’єднані до цієї ж лінії.

Його призначення полягає у можливості підключати кілька пристроїв до однієї спільної шини даних. Наприклад, у комп’ютері багато компонентів можуть використовувати одну й ту саму шину для передачі інформації, але лише один із них у конкретний момент має право виводити дані. Інші пристрої переводяться у стан Hi-Z, щоб уникнути конфлікту сигналів (ситуації, коли один пристрій подає «1», а інший одночасно «0»).

Таким чином, трьохстановий драйвер виконує роль «керованого перемикача», який дозволяє організувати спільну роботу декількох джерел сигналу на одній лінії, забезпечуючи правильну синхронізацію і запобігаючи пошкодженню компонентів через сигналові конфлікти.

Зберігання цифрової інформації в пам'яті

Пам'ять — це сукупність апаратних елементів комп'ютера, в яких ми зберігаємо інформацію. У більшості комп'ютерів на сучасному ринку кожна комірка пам'яті містить один байт інформації, і кожен байт має унікальну послідовну адресу. Пам'ять називається байт-адресовуваною, оскільки кожен байт має окрему адресу. Адреса комірки пам'яті визначає її фізичне розташування, а її вміст – це дані. Коли ми записуємо в пам'ять, ми вказуємо адресу та 8, 16 або 32 біти даних, що призводить до збереження цієї інформації в пам'яті.

Зазвичай дані передаються з процесора в пам'ять під час циклу запису. Коли ми читаємо з пам'яті, ми вказуємо адресу, що призводить до отримання з пам'яті 8, 16 або 32 бітів даних. Зазвичай дані надходять з пам'яті в процесор під час циклу читання. Постійний запам'ятовуючий пристрій (ПЗП, ROM) – це тип пам'яті, в якій інформація запрограмована або записана в пристрій, і під час нормальної роботи дозволяється лише читання. Оперативна пам'ять (ОЗП, RAM) використовується для зберігання тимчасової інформації, і під час нормальної роботи ми можемо читати з оперативної пам'яті або записувати дані в неї. Інформація в ПЗП є енергонезалежною, тобто її вміст не втрачається після відключення живлення. Натомість інформація в оперативній пам'яті є енергонезалежною, тобто її вміст втрачається після відключення живлення. Система може швидко та зручно зчитувати дані з ПЗП. Програмування або запис даних у ПЗП займає порівняно багато часу. Запис у флеш-ПЗП – це двоетапний процес. Спочатку ПЗП стирається, в результаті чого всі біти стають 1. По-друге, система записує нулі в ПЗП за потреби. Кожен з цих двох кроків займає близько 1 мс. Натомість, зчитування даних з оперативної пам'яті та запис даних у неї є швидким та простим. Запис в оперативну пам'ять відбувається приблизно в 100 000 разів швидше (близько 10 нс). З іншого боку, ПЗП набагато щільніша за оперативну пам'ять. Це означає, що ми можемо вмістити в чіп більше бітів ПЗП, ніж бітів оперативної пам'яті. Більшість мікроконтролерів мають набагато більше ПЗП, ніж оперативної пам'яті.

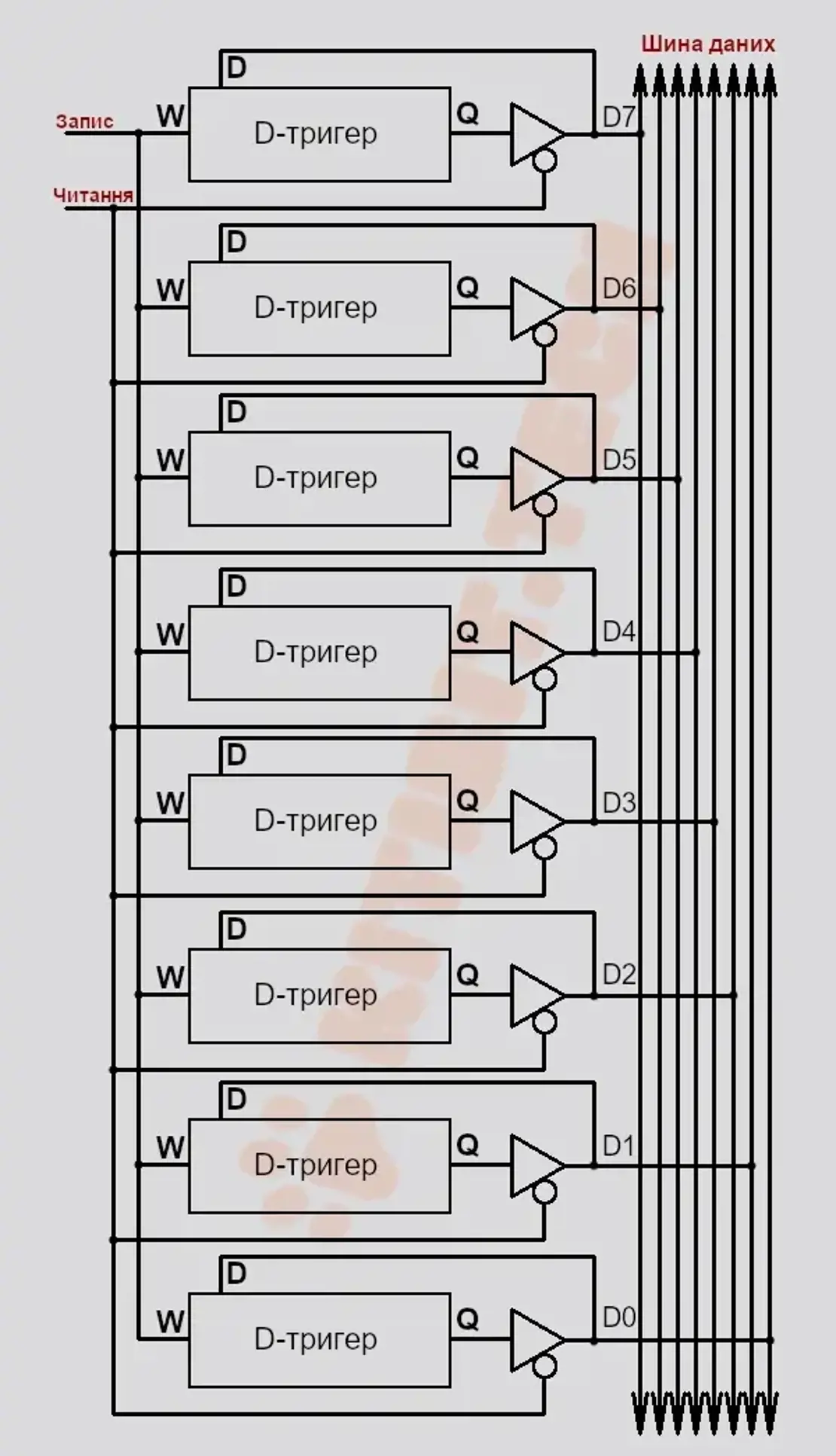

Можна побудувати 8-бітний запам'ятовуючий елемент шляхом комбінування 8 тригерів. Цей базовий запам'ятовуючий елемент називається регістром.

Шина — це сукупність проводів, що використовуються для передачі даних з одного місця в інше. У цій схемі сигнали D7–D0 представляють шину даних. Сучасні регістри на мають 32-бітну, або 64-бітну ширину, але для простоти в цьому прикладі ми показуємо 8-бітний регістр. Ми називаємо його пам'яттю, тому що доки схема залишається під напругою, цифрова інформація, представлена вісьмома напругами Q7–Q0, буде зберігатися. З регістром виконуються дві операції: запис і читання. Щоб виконати запис, спочатку потрібно помістити потрібну інформацію на 8 проводів шини даних (D7–D0). Як видно на схемі, ці сигнали шини даних присутні на входах D 8 тригерів. Далі система генерує імпульси сигналу запису то високий, то низький рівень. Цей імпульс запису зафіксує ці дані у 8 тригерах. Операція читання розмістить копію інформації регістра на шині даних. Зверніть увагу, що сигнали затвора трьохстанових драйверів мають негативну логіку. Це означає, що якщо сигнал "Читання" високий, трьостанові драйвери вимкнені, і цей регістр не впливає на сигнали на шині. Однак операція читання відбувається шляхом встановлення сигналу "Читання" низького рівня, що розмістить дані регістра на шині.

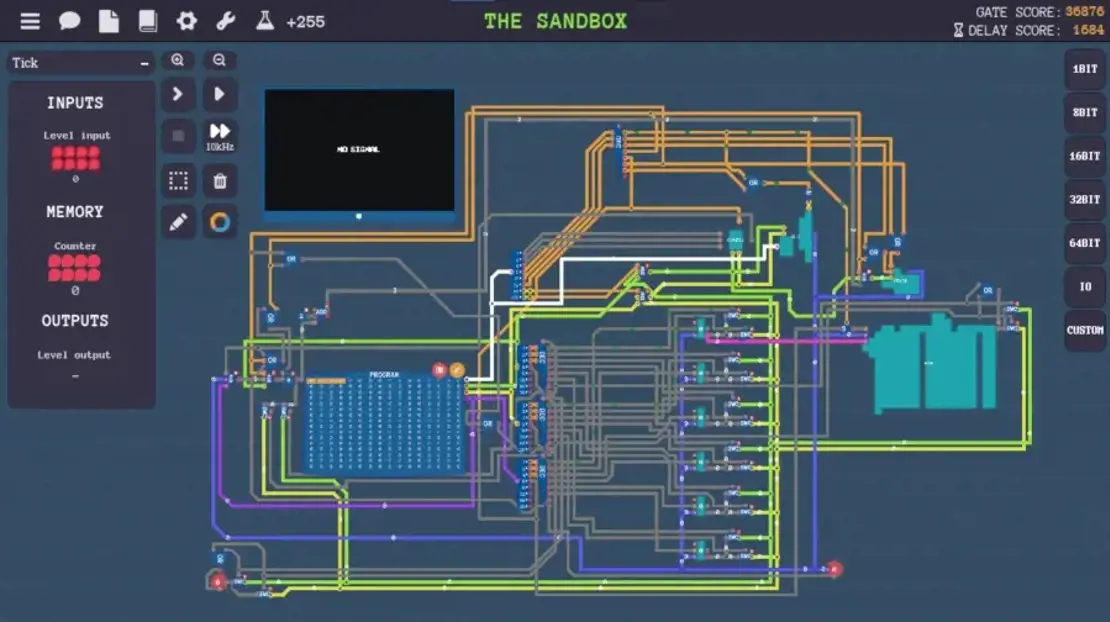

На завершення хочу порекомендувати чудову гру Turing Complete - це головоломка, де ви крок за кроком будуєте комп'ютер з логічних елементів. Це можливість глибоко зазирнути в цифрову логіку і самому розробити цифрову машину в ігровій манері. Гру можна купити в Steam і коштує вона зовсім недорого. На зображенні вище представлена моя схема - результат проходження гри 😉